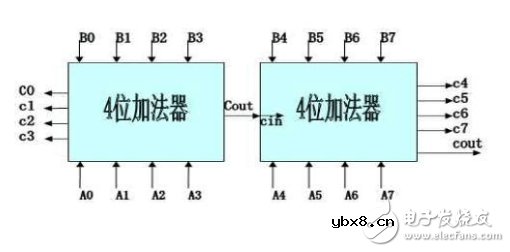

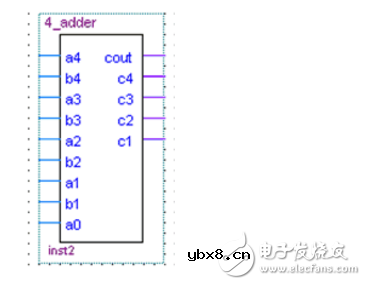

8位全加器可由2个4位的全加器串联组成,因此,先由一个半加器构成一个全加器,再由4个1位全加器构成一个4位全加器并封装成元器件。加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin相接最高位的输出即为两数之和。最后一个Cout输出进位,D8显示。

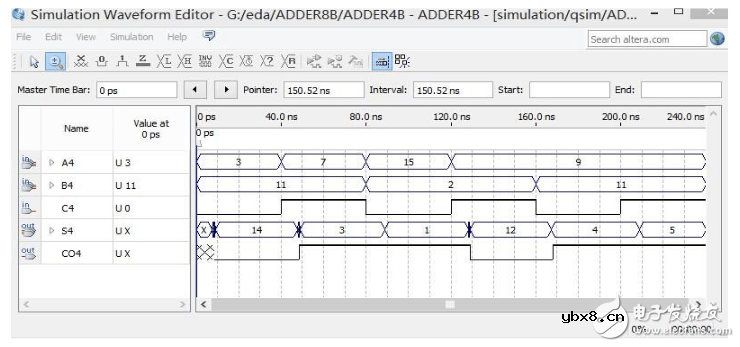

1、建立波形文件。为此设计建立一个波形测试文件。选择File项及其New,再选择右侧New窗中的vector Waveform file项,打开波形编辑窗。

2、输入信号节点。在波形编辑窗的左方双击鼠标,在出现的窗口中选择Node finder,在弹出的窗口中首先点击List键,这时左窗口将列出该项设计所以利用中间的“=》”键将需要观察的信号选到右栏中。

3设定仿真时间宽度。选择edit项及其End time选项,在End time选择窗中选择适当的仿真时间域,本次实验由于是八位的全加器,为避免延迟太大不利于显示,可将End Time 设置为50ms,以便有足够长的观察时间和便于分析的波形仿真波形图。

4、波形文件存盘。选择File项及其Save as选项,按OK键即可。存盘窗中波形文件名是默认的(这里是adder.scf所以直接存盘即可。

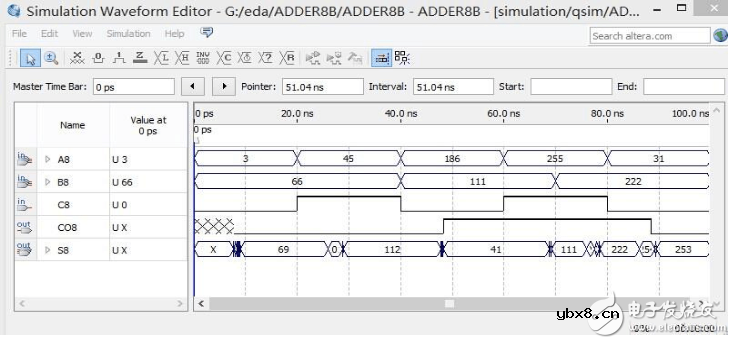

5、运行仿真器。点击processing中的Start simulation选项,如图是仿真运算完成后的时序波形。注意,刚进入如图所示的窗口时,应该将最下方的滑标拖向最左侧,以便可观察到初始波形。

1.首先为此工程建立一个放置与此工程相关的所有文件的文件夹,认为工作库(Work Library)。本项设计我的文件夹取名为8位全加器。

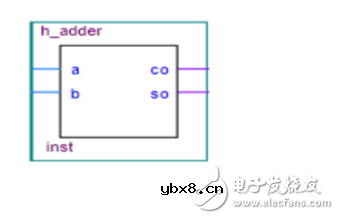

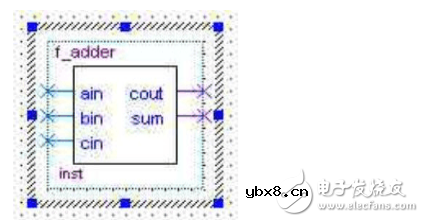

2. 选FileNew,在弹的New对话框中选择Device Design Files 页的原理图文件编辑输入项Block diagram\Schematic File,画半加器原理图。 3. 另存自己的工程,将已设计好的图文件命名为:h_adder.bdf,并保存在此文件夹内。编译通过之后,将该半加器封装入库待设计1位全加器的时候调用。

4. 利用封装后的半加器画1位的全加器,并封装成元器件。

5. 利用封装后的1位全加器,将4个1位全加器串行,画4位的全加器,并封装成元器件。

6. 将2个4位全加器元器件串行,按照实验原理设计8位全加器。

7.运行并调试成功。

8. 锁引脚,

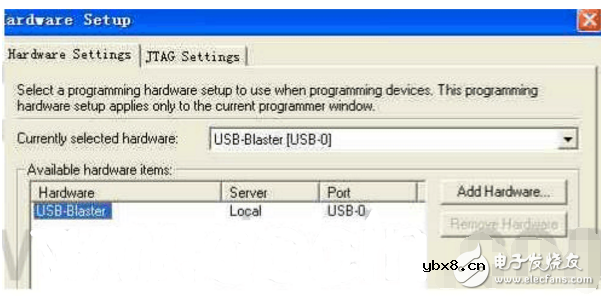

9. 连接USB。

按START运行。

4位二进制并行加法器的源程序ADDER4B.VHD --ADDER4B.VHD LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER4B IS

PORT(C4: IN STD_LOGIC;

A4: IN STD_LOGIC_VECTOR(3 DOWNTO 0); B4: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

S4: OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4: OUT STD_LOGIC); END ENTITY ADDER4B;

ARCHITECTURE ART OF ADDER4B IS

SIGNAL S5: STD_LOGIC_VECTOR(4 DOWNTO 0); SIGNAL A5, B5: STD_LOGIC_VECTOR(4 DOWNTO 0); BEGIN

A5《=‘0’& A4; B5《=‘0’& B4; S5《=A5+B5+C4;

S4《=S5(3 DOWNTO 0); CO4《=S5(4);

END ARCHITECTURE ART; --ADDER8B.VHD LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ADDER8B IS

PORT(C8:IN STD_LOGIC;

A8:IN STD_LOGIC_VECTOR(7 DOWNTO 0); B8:IN STD_LOGIC_VECTOR(7 DOWNTO 0); S8:OUT STD_LOGIC_VECTOR(7 DOWNTO 0); CO8:OUT STD_LOGIC); END ENTITY ADDER8B;

ARCHITECTURE ART OF ADDER8B IS COMPONENT ADDER4B IS PORT(C4:IN STD_LOGIC;

A4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); B4:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S4:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); CO4:OUT STD_LOGIC); END COMPONENT ADDER4B; SIGNAL SC:STD_LOGIC; BEGIN

U1:ADDER4B

PORT MAP(C4=》C8,A4=》A8(3 DOWNTO 0),B4=》B8(3 DOWNTO 0), S4=》S8(3 DOWNTO 0),CO4=》SC); U2:ADDER4B

PORT MAP(C4=》SC,A4=》A8(7 DOWNTO 4),B4=》B8(7 DOWNTO 4), S4=》S8(7 DOWNTO 4),CO4=》CO8); END ARCHITECTURE ART;

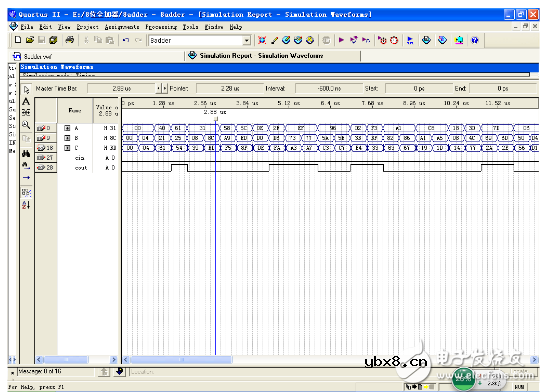

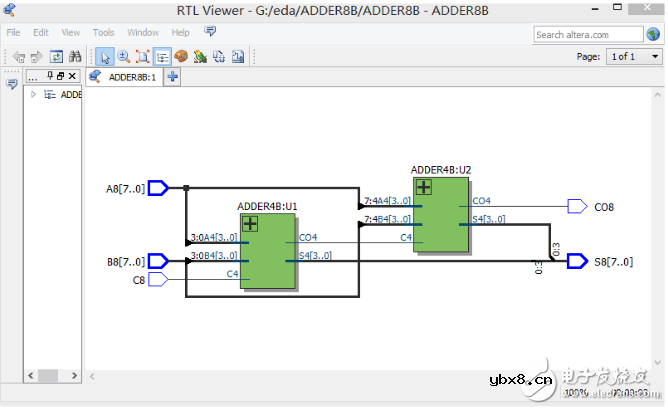

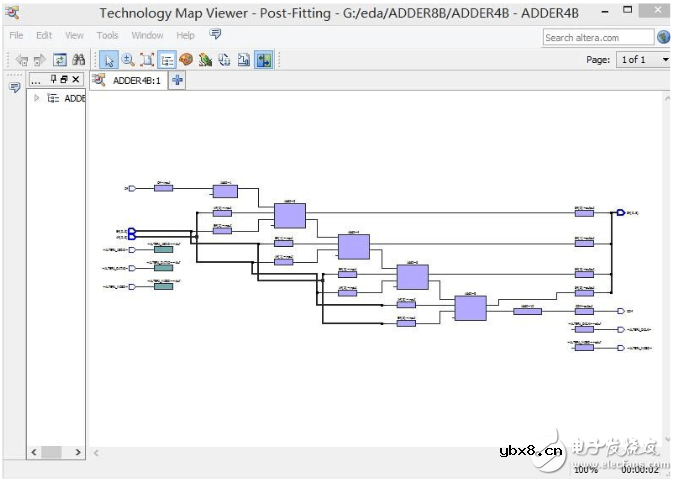

在程序调试和仿真时,我们要使用自底向上的方法进行,也就是对于含有多个模块的设计,我们要先从底层模块进行调试和仿真,再进行更高层次模块的调试和仿真,最后进行顶层模块的调试与仿真。下图分别使用Quartus II 8.0对ADDER4B和ADDER8B进行时序仿真的结果。

ADDER4B的时序仿真结果

ADDER8B的时序仿真结果

下面是使用Quartus II 8.0进行逻辑综合ADDER8B的RTL视图;对ADDER8B的RTL视图中ADDER4B进行展开的视图;使用Quartus II 8.0对ADDER8B进行逻辑综合后的资源使用情况

ADDER8B综合后的RTL视图

ADDER8B综合后的RTL视图中将ADDER4B展开后的视图

相关热词:#加法器

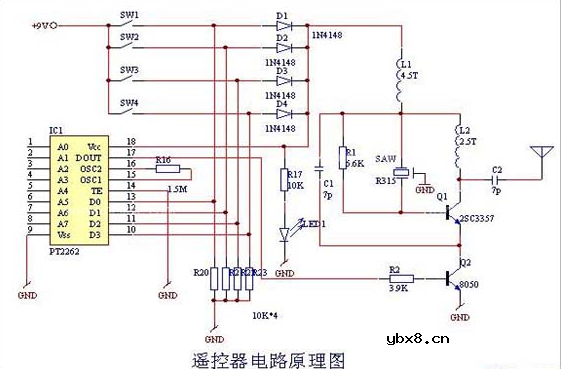

无线遥控器电路图制作

无线遥控器电路图制作

时间:2026-03-07

无线电遥控门铃电路原理图

无线电遥控门铃电路原理图

时间:2026-03-07

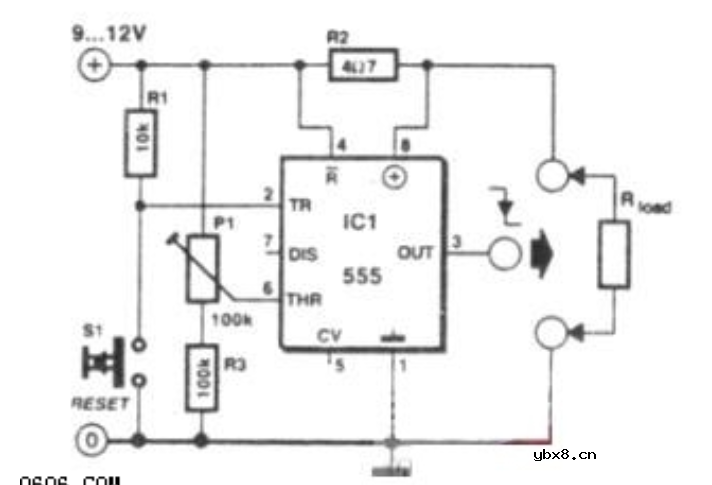

NE555过流保护检测器电路图

NE555过流保护检测器电路图

时间:2026-03-07

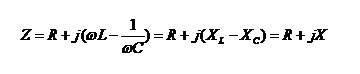

串联谐振升压原理

串联谐振升压原理

时间:2026-03-07

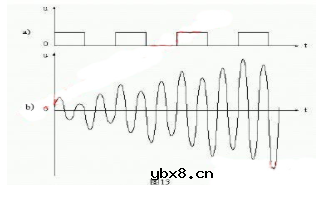

谐振回路的工作原理

谐振回路的工作原理

时间:2026-03-07

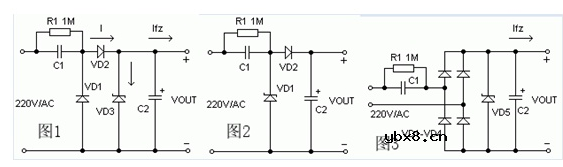

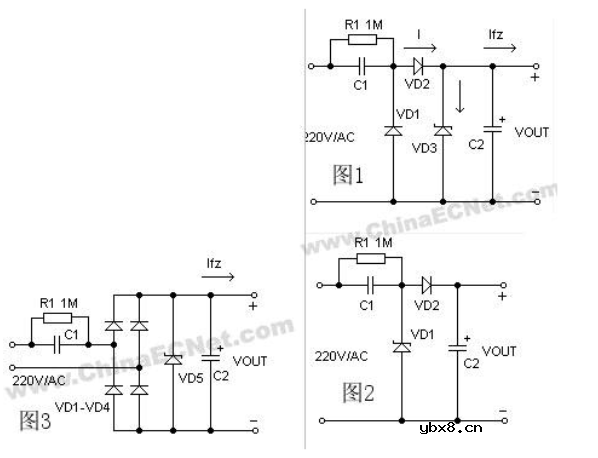

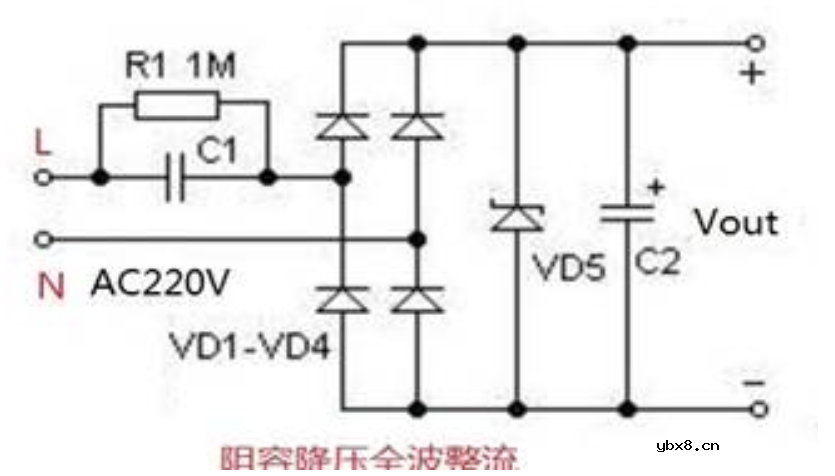

电容降压电路原理

电容降压电路原理

时间:2026-03-07

实用的电容降压电路

实用的电容降压电路

时间:2026-03-07

低成本的阻容降压电路原理图分析

低成本的阻容降压电路原理图分析

时间:2026-03-07

阻容降压原理及电路

阻容降压原理及电路

时间:2026-03-07

阻容降压电路的误区

阻容降压电路的误区

时间:2026-03-07

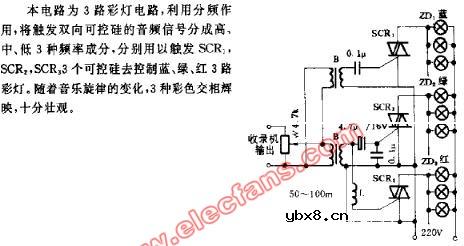

彩灯电路

彩灯电路

时间:2026-03-05

三相异步电动机原理

三相异步电动机原理

时间:2026-03-04

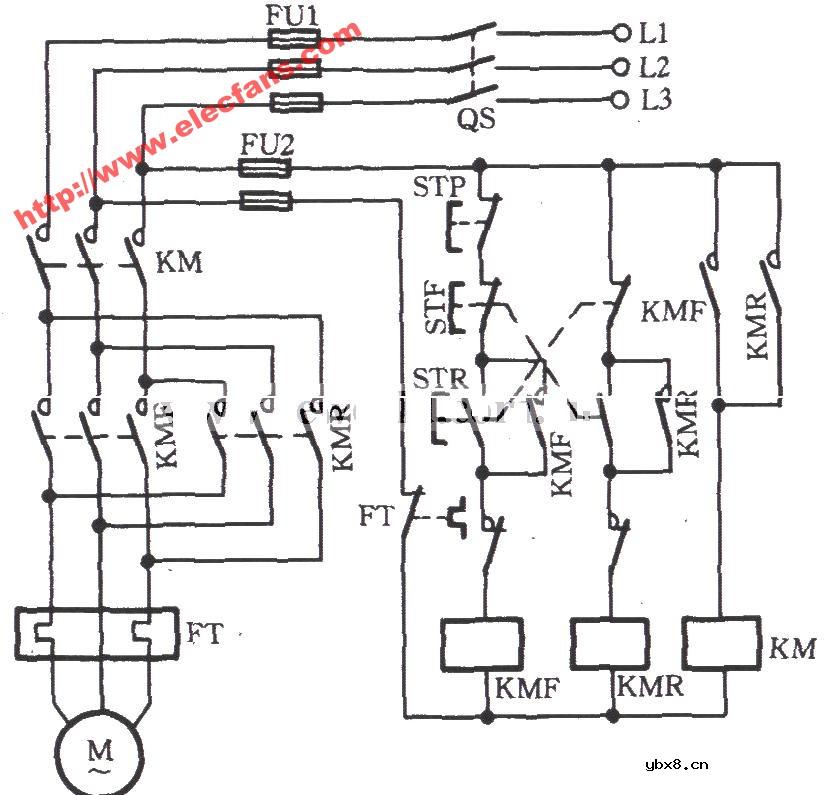

电动机单线远程正反转控制电路图

电动机单线远程正反转控制电路图

时间:2026-03-04

三相异步电动机的七种调速方式

三相异步电动机的七种调速方式

时间:2026-03-04

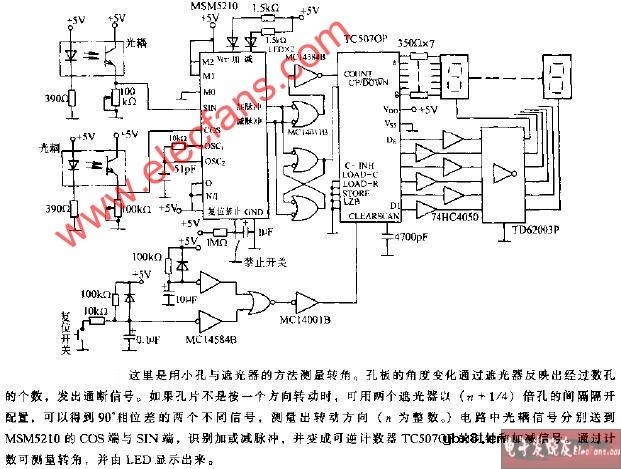

转角测量电路

转角测量电路

时间:2026-03-05

经典的正弦波发生电路

经典的正弦波发生电路

时间:2026-03-05

三相异步电动机的拆装详讲

三相异步电动机的拆装详讲

时间:2026-03-04

USB转232电路图

USB转232电路图

时间:2026-03-04

电度表的工作原理

电度表的工作原理

时间:2026-03-04

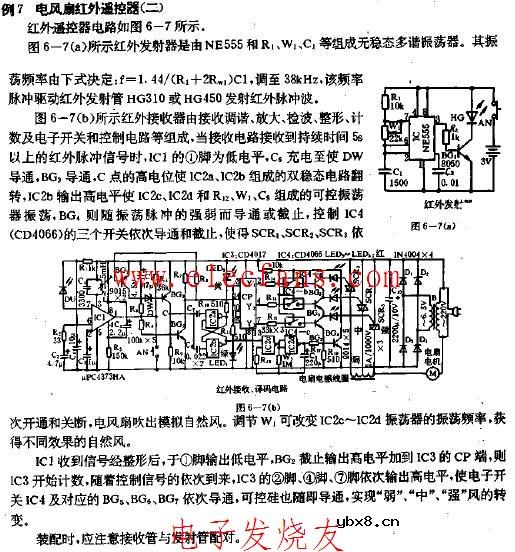

电风扇红外遥控器2

电风扇红外遥控器2

时间:2026-03-04