FPGA开发基本流程包括:设计输入、设计仿真、设计综合、布局布线,它们的连接关系如图1 所示。

图1 FPGA 开发流程图

设计综合是整个FPGA 设计流程中一个重要的步骤,它将HDL 代码生成用于布局布线的网表和相应的约束。而且随着新一代FPGA 芯片频率和密度的增长,时序收敛问题越来越严重,综合已经成为整个设计成败的关键。通常芯片供应商的FPGA 软件中都包含综合功能,但它相对简单,不能适应新一代FPGA 芯片的发展,需要更加专业的综合工具来优化设计,Precision RTL 综合就是其中之一。

相关热词:#电子电路图

2017.2.09讲解:启动停止自锁控制回路视频

2017.2.09讲解:启动停止自锁控制回路视频

时间:2026-03-12

2017.2.11电动机单向电气控制原理图接线与讲...

2017.2.11电动机单向电气控制原理图接线与讲...

时间:2026-03-12

变压器常见故障你知道哪些? 老师教你解决办...

变压器常见故障你知道哪些? 老师教你解决办...

时间:2026-03-12

低压配电柜是什么, 老师带你认识配电柜的知...

低压配电柜是什么, 老师带你认识配电柜的知...

时间:2026-03-12

电工们你们知道配电箱和配电柜的区别吗, 老...

电工们你们知道配电箱和配电柜的区别吗, 老...

时间:2026-03-12

培训课程电工基础第1课: 电工安全视频

培训课程电工基础第1课: 电工安全视频

时间:2026-03-12

高压一次主要电器元件的介绍, 看完你就懂视...

高压一次主要电器元件的介绍, 看完你就懂视...

时间:2026-03-12

高压柜测量回路原理, 你懂多少看我来教你视...

高压柜测量回路原理, 你懂多少看我来教你视...

时间:2026-03-12

不接地系统接地电阻计算, 希望大家喜欢视频

不接地系统接地电阻计算, 希望大家喜欢视频

时间:2026-03-12

阅读二次回路的基本方法第一集视频

阅读二次回路的基本方法第一集视频

时间:2026-03-12

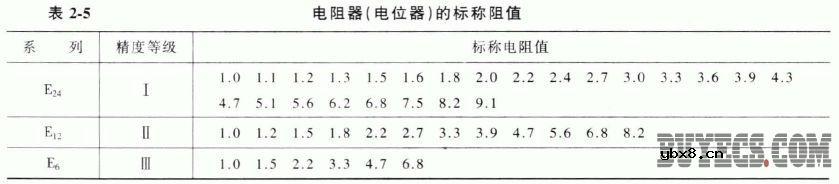

电阻的标称阻值和允许偏差

电阻的标称阻值和允许偏差

时间:2026-03-05

玻璃釉电容器的结构与特点

玻璃釉电容器的结构与特点

时间:2026-03-05

压敏电阻有正负极吗

压敏电阻有正负极吗

时间:2026-03-05

变压器并列运行的条件浅析

变压器并列运行的条件浅析

时间:2026-03-06

电容器入门教程

电容器入门教程

时间:2026-03-05

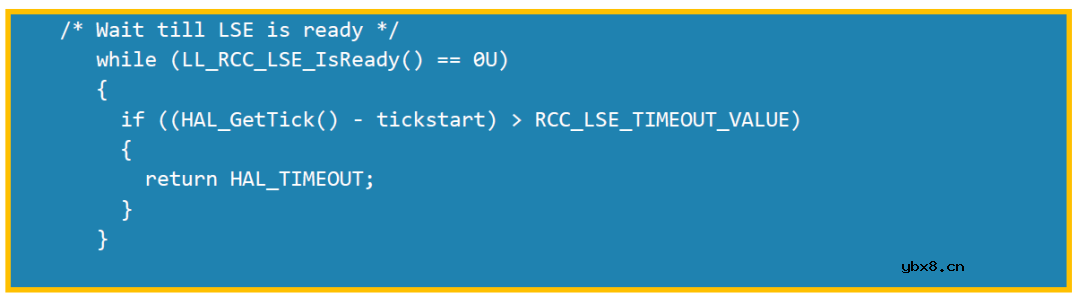

关于STM32WL LSE 添加反馈电阻后无法起振的...

关于STM32WL LSE 添加反馈电阻后无法起振的...

时间:2026-03-05

电容的作用和工作原理 电容具有什么特点 简...

电容的作用和工作原理 电容具有什么特点 简...

时间:2026-03-05

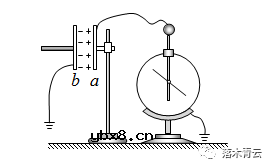

可调电阻怎么接线

可调电阻怎么接线

时间:2026-03-05

压敏电阻坏了怎么替代

压敏电阻坏了怎么替代

时间:2026-03-05

压敏电阻爆裂的原因分析

压敏电阻爆裂的原因分析

时间:2026-03-05